產品動態

- 群創12.1寸 G121ICE-LM2 對比度1000:1 常

- G270QAN01.4 友達27寸 400 cd/m2 分辨率2

- G190ETT01.1 友達19寸 分辨率1280*1024

- 18.5寸G185HAT01.1 友達 對比度1000:1 分

- 友達G101EAT02.6 10.1寸 分辨率1280*800

- G156HAN02.303 友達15.6寸 對比度1000:1

- G057QAN01.1 友達5.7寸 常黑顯示 1000:1

- G238HAN04.0 友達23.8寸 常黑顯示 分辨

- 友達8.4寸 G084SAN01.0 常黑顯示 分辨

- G057QAN01.0 友達 5.7寸 500 cd/m2 常黑

全國統一服務熱線:

15382323032

客服QQ:3234659108

手機:15382323032

地址:浙江省杭州市余杭區五常街道西溪軟件園金牛座B2座4層4118-4119

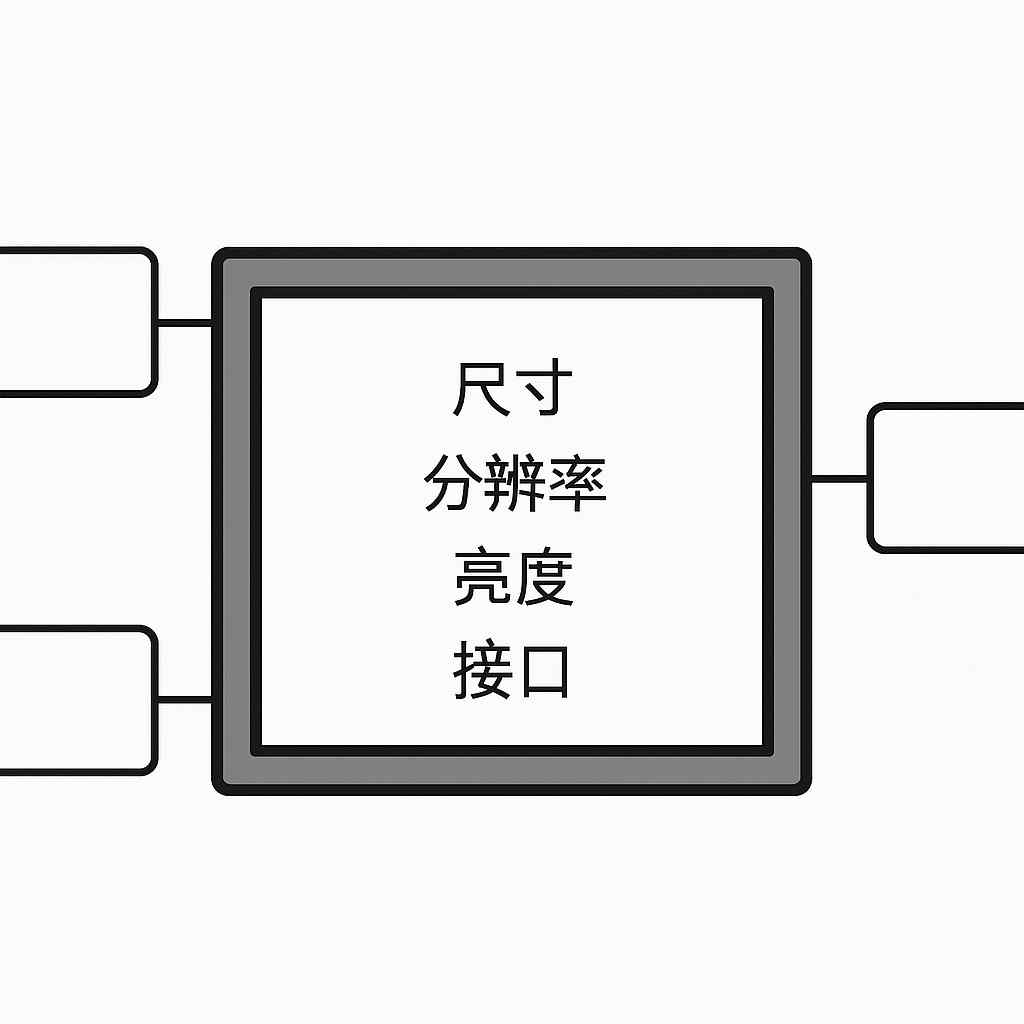

RGB還是LVDS?LCD工業液晶屏幕信號傳輸選型

在工業設備里做顯示,很多項目卡在“信號怎么從主板送到屏上”。同一塊液晶屏,換一種傳輸方式,現場穩定性、EMI整改成本、線束復雜度、甚至后期可維護性都會完全不同。RGB(并行RGB/TTL)與LVDS(面板常用的FPD-Link/OpenLDI一類LVDS鏈路)看起來都是“把像素送到LCD液晶屏”,但它們的工程屬性幾乎是兩個世界:一個靠多根單端并行線同步像素節拍,另一個靠低擺幅差分對把數據串行化再送過去。

精顯從工業應用最關心的維度——抗干擾、線束與連接器、可達帶寬、布線難度、成本與維護、以及常見踩坑點——做系統對比,并給出液晶模組在不同場景下的選擇建議。

一、“RGB”和“LVDS”到底指什么

1、RGB:并行RGB/TTL

在很多MCU/MPU里,RGB接口本質是并行像素總線:每個像素用若干根數據線同時輸出,配合像素時鐘與行場同步信號,把像素節拍“喂”給面板的TCON(TimingController)。典型信號包括像素時鐘(PIXCLK/LCD_CLK/DOTCLK)、HSYNC、VSYNC、DE(DataEnable),以及RGB數據位(如18位或24位數據線)。NXP的應用筆記在描述LCD面板接口時明確指出面板需要HSYNC、VSYNC、DE、PIXCLK及完整RGB數據線。

ST的LTDC(LCD-TFTDisplayController)介紹文檔也說明控制信號(HSYNC、VSYNC、DE)以及像素時鐘可配置極性,并用于驅動LCD-TFT顯示。

可以把它理解成:RGB是“并行+同步時鐘”的裸像素輸出,線很多,時序靠主控持續輸出。

2、LVDS:面板接口中常說的LVDS

LVDS首先是一套電氣標準(TIA/EIA-644/644A定義的低電壓差分信號接口)。TI的設計指南提到LVDS相關標準由ANSI/TIA/EIA-644A等規格定義。

在顯示行業里,“LVDS屏”往往不是指“任意LVDS差分線”,而是指一種成熟的面板鏈路(常見被稱為FPD-Link/OpenLDI/PanelLink一類):把并行RGB與控制信號序列化后,用若干組差分對(數據對+時鐘對)送到液晶模組端再反序列化。典型的單像素24bpp映射是4條LVDS數據對+1條LVDS時鐘對(4D+C)。TI的FPD-Link器件資料明確寫到“24位RGB+控制信號序列化后通過4data+clock(4D+C)LVDS接口輸出”。

可以把它理解成:LVDS在面板場景里經常代表“差分序列化鏈路”,線更少、擺幅更小、抗干擾更強,但對差分布線與端接更敏感。

二、為什么LVDS更適合“工業抗干擾”

工業現場最常見的敵人是:長線束、地電位差、開關電源紋波、變頻器、電機啟停的共模干擾、靜電放電。RGB與LVDS在電氣層面的差異,決定了它們面對這些問題時的“底子”。

1、LVDS的典型電壓擺幅與共模

以TI的LVDS器件描述為例,常見LVDS輸出差分擺幅是約350mV(100Ω負載),共模輸出電壓典型在1.2V附近。TI多份資料都提到LVDS驅動器典型共模1.2V、差分擺幅350mV。

同時,LVDS標準一致性指標中,器件說明也給出符合TIA/EIA-644的最低差分輸出電壓量級(例如最小247mV)等信息。

這意味著LVDS是“低擺幅+電流驅動+差分”的組合:對外輻射更小,對共模噪聲更不敏感,且在地電位差存在時更有容忍度(不少器件會在規格里說明可承受一定的地電位差)。

2、RGB并行接口的典型特征

RGB并行接口的信號(數據線、時鐘、同步)通常是單端CMOS/TTL電平。它靠像素時鐘邊沿去采樣并行數據,線多且彼此緊密相關:任何一根線的串擾、過沖、地彈、時序偏斜,都可能在屏上表現為抖動、閃點、偶發花屏或邊緣噪點。由于它不是差分結構,對地參考與回流路徑更敏感,線束一長、環境一吵,就更難控。

在工業設備中,這個差異會直接轉化為:

1·RGB更容易在EMI整改里“被動挨打”(要靠屏蔽、地設計、走線等慢慢補)

2·LVDS更像“先天抗性更強”(但也要做到差分對阻抗、端接、走線規則)

三、帶寬與可用分辨率

RGB與LVDS誰更能扛“高分辨率/高刷新”,這里要先糾正一個常見誤解:很多人以為“RGB是并行的,所以一定更快”。工程上并不總是這樣,因為速度瓶頸往往不在“單根線快不快”,而在線數、走線匹配、連接器與線束可實現性。

1、RGB:每個像素周期并行吐出一個像素

NXP關于RGB并行接口的說明提到:并行數據接口“1個時鐘周期需要24位(或其他格式)表示1個像素”。

也就是說,RGB接口的“帶寬”主要取決于你能跑多高的像素時鐘,以及你的板級/線束能否保證這些線在該頻率下滿足時序裕量。

優點:協議簡單、直觀;

代價:線數暴漲,時序收斂困難,越高像素時鐘越難做可靠。

2、LVDS:序列化后走差分對

面板常用的LVDS鏈路(如FPD-Link/OpenLDI類)把24位RGB等信號序列化后輸出,典型是4D+C。

序列化的好處是:線更少,且差分傳輸更適合高速與更長連接;因此它在大量中尺寸工業液晶屏上成為主流接口之一。

TI的某些FPD-Link序列化器資料還會給出吞吐指標。

對工業應用而言,這類來源能幫助你在官網解釋:“為什么同樣分辨率,LVDS更容易實現穩定傳輸”。

四、線束與連接器

1、RGB的線數:

數據線+時序線,少則二十多根,多則三十多根以常見24位RGB為例:

1·數據線:R/G/B共24根

2·時序:PIXCLK、HSYNC、VSYNC、DE(以及可能的復位、背光控制等)

NXP應用筆記中展示的示例接口用到18位RGB數據線(DISPB_DATA[17:0])以及HSYNC、VSYNC、DE、PIXCLK。

如果你做24位,就更“粗壯”。這直接帶來:更寬的FPC/FFC、更多針腳連接器、更復雜的線束、更多回流與串擾處理工作。

2、LVDS的線數:

差分對為單位,常見4D+C(5對)或更少/更多(取決于位寬與鏈路)TIFPD-Link文檔明確給出4data+clock(4D+C)的典型結構。

對比RGB的二三十根單端線,LVDS往往在連接器、排線寬度、線束裝配一致性上更有優勢。

工業項目的現實經驗是:

1·線越多,裝配出錯率越高,批量一致性越難控

2·線越少、差分越規范,工藝窗口越大

五、為什么很多工業液晶模組“越到現場越像玄學”

1、LVDS的EMI優勢有明確來源依據

TI關于LVDS技術的概述提到:由于信號擺幅更小,LVDS相較傳統CMOS/TTL等能減少EMI影響,原因包括電流模式驅動、軟轉換、低開關電流和真正的差分傳輸。

TI在FPD-Link介紹中也提到LVDS在EMI方面相較其他技術有優勢,強調其較低的譜內容(EMI)。

2、RGB的EMI挑戰:

RGB并行接口的像素時鐘會帶著大量高頻能量,數據線同時翻轉會形成較大的瞬時電流與回流壓力。線束一長,等效成“天線”,很容易引入輻射/傳導問題,現場與實驗室差異也會變大(現場地線、機殼接地、線束走向更不可控)。

因此很多工業項目最終的選擇邏輯會變成:

1·若是板對板、距離很短、結構緊湊,RGB仍然可控

2·若存在跨板連接、線束繞行、干擾源豐富,LVDS往往更穩

六、布線與調試難度:

RGB難在“時序一致”,LVDS難在“差分鏈路規范”

1、RGB:你要對每一根線負責

RGB并行口的核心難點是時序:像素時鐘到來時,數據必須在建立/保持時間窗口內穩定。線多意味著:

每根線的長度差帶來偏斜

串擾帶來波形畸變

回流路徑不佳帶來地彈

如果再疊加“屏端TCON對時序要求比較緊”,你會在調試階段花大量時間在波形與時序裕量上。

2、LVDS:對差分對、端接與阻抗負責

LVDS常用100Ω差分端接,差分對要匹配長度與阻抗,走線需要控制耦合、過孔與參考平面完整。好處是通道少,規則清晰;難點是高速差分不允許“隨便畫”,連接器、FFC、轉接板都可能成為瓶頸。

從工程管理角度看:

RGB是“線太多,問題太分散”

LVDS是“線少但每條都要按規范來”

七、可靠性與維護

1、可替換性:接口決定你能否“換屏不換板”

很多LCD液晶屏型號會在生命周期里更新。RGB接口對面板時序參數敏感(行場、極性、像素時鐘、DE模式等),換屏往往意味著重新核對一套時序;LVDS面板也同樣需要匹配映射與時序,但行業里LVDS面板生態更成熟,很多替代料遵循相近鏈路規范,系統的適配空間相對更大(前提是你預留了驅動與映射的彈性)。

2、抗環境:震動、粉塵、氧化、松動

線束越多、針腳越多,長期震動與氧化帶來的接觸風險越大。LVDS用更少的差分對,連接器針腳數更小,在“裝配一致性”上通常更占優。

八、把“接口選型”變成可落地的決策

下面給出一套工業項目里非常實用的選擇邏輯,你可以直接寫進官網“選型指南”,也適合業務同事拿去溝通客戶。

1、優先考慮RGB的典型場景

1·主板與液晶模組距離極短(板對板/短FPC),結構緊湊

2·分辨率不高或像素時鐘可控,且對EMI約束沒那么苛刻

3·主控自帶成熟RGB/LTDC接口,軟件棧與團隊經驗更偏RGB

4·希望鏈路簡單直觀,調試資源(示波器、邏輯分析)足夠

RGB接口的信號組成與時序在NXP、ST等主控文檔中都有明確描述,適合做標準化配置與驗證。

2、優先考慮LVDS的典型場景

1·需要跨板連接、線束更長、環境干擾更強

2·需要更好的EMI表現,減少整改成本

3·分辨率與刷新提升后,RGB的并行線束與時序收斂成本過高

4·產品要做更強的批量一致性與可維護性

LVDS在電氣擺幅與EMI方面的優勢有明確技術依據(低擺幅差分),面板鏈路(如FPD-Link)對24位RGB常見4D+C結構也有清晰的行業實現。

3、接口選擇要和結構形態綁定

很多項目不是因為“接口理論上不行”失敗,而是因為結構讓它變得不可控:

1·想用RGB,但屏在門板上、主板在機箱里,中間一根長排線繞來繞去

2·想用LVDS,但轉接板太多、連接器沒選對、差分對被迫繞線且參考地不連續

接口選型時,把“線束長度、走線路徑、連接器形態、接地方案”一起寫進評審,往往能少走一半彎路。

九、建議做這些測試

為了讓“選型”變成可驗證的結論,而不是主觀判斷,建議你建立接口驗證清單:

1·信號完整性:關鍵邊沿、過沖/欠沖、抖動、差分眼圖(LVDS)

2·EMI預評估:整機在典型工作模式下的輻射/傳導趨勢

3·溫度與老化:高低溫下花屏/閃爍概率、連接器接觸穩定性

4·抗擾度:電機啟停、繼電器吸合、ESD點放對畫面影響

5·批量一致性:至少三套樣機/小批試產復現概率

尤其在工業場景,“穩定性”是第一指標,參數再漂亮,現場不穩就是返工成本。

十、常見問題

Q1:RGB接口不是并行的嗎,為什么反而更容易出問題?

并行本身不等于容易。RGB需要二三十根單端線在同一像素節拍下協同工作,任何一根線的偏斜、串擾、回流不良都可能破壞采樣窗口。它的難點在“線太多、時序太緊”,尤其當線束變長、環境變吵時更明顯。

Q2:LVDS為什么更適合工業抗干擾?有數據依據嗎?

LVDS典型差分擺幅約350mV、共模約1.2V,屬于低擺幅差分傳輸。相關技術資料指出,小擺幅與差分傳輸可降低EMI,并減少對共模干擾的敏感度。

Q3:面板說“LVDS接口”,就是TIA/EIA-644標準嗎?

電氣層面往往遵循LVDS(TIA/EIA-644/644A)一類標準的擺幅與閾值要求;但在顯示行業,“LVDS屏”常常還包含特定的面板鏈路格式(例如FPD-Link/OpenLDI映射)。因此選型時既要確認電氣兼容,也要確認通道數、位寬映射與時序。

Q4:LVDS是不是就一定能走很長線?能走多遠?

標準本身不直接給出統一的“米數”,距離取決于數據速率、線纜類型、端接、損耗與EMI環境。工程上LVDS通常比并行RGB更適合跨板和更長連接,但要按差分鏈路規范做線材與端接,并在目標線長上做實測驗證。

Q5:我已經選了RGB屏,后期發現EMI難控,還有補救空間嗎?

有,但成本會逐步上升。常見思路包括:縮短RGB線束、加強地參考與回流、優化走線與串擾、增加屏蔽與濾波、降低像素時鐘或刷新策略、結構上調整線束路徑。若結構允許,評估把并行RGB轉換為LVDS再走線,也是一條常見的工程路線(需要額外的序列化/反序列化器件)。

最新資訊

- 2026-02-10 15.6寸LCD工業液晶屏1000高亮度屏功

- 2026-02-06 LCD10.1寸工業液晶屏常見問題:分

- 2026-02-05 精顯科技2026年春節假期安排通知

- 2026-02-05 8寸工控LCD液晶屏尺寸一樣但孔位

- 2026-02-04 TFT-LCD工業液晶屏型號后綴怎么看

- 2026-02-03 京瓷TCG057VGLGC-G50-S帶觸摸一體液晶

- 2026-02-02 LCD液晶屏觸摸屏蓋板玻璃如何選?

- 2026-01-30 LCD工業液晶屏G104系列怎么選?G104S

- 2026-01-29 LCD工業液晶屏顯示器花屏/閃屏/白

- 2026-01-28 15.6寸LCD工業液晶屏:常見接口是eD